”数字密码锁 verilog“ 的搜索结果

2.密码长度位6位,复位后初始密码位“666666”,开锁方式:xxxxxx#(x代表密码数字),密码设置方式:*yyyyyy*yyyyyy*(y为旧密码,输入两次,正确/错误时用数码管提示),然后输入#xxxxxx#xxxxxx#(x为新密码,输入两次...

代码功能: 电子密码锁 1、密码为4位 2、内置默认密码,可以修改密码 3、密码输入错误3次报警

代码功能: 数字密码锁 1、有改密码功能 2、密码错误三次报警灯闪烁 3、通过按键输入密码

1、设计一个密码锁的控制电路,当输入正确代码时,输岀开锁信号用红灯亮、绿灯 熄灭表示关锁,用绿灯亮、红灯熄灭表示开锁 2、在锁的控制电路中储存一个可以修改的4位代码,当开锁按钮开关的输入代码 等于储存代码时,...

哈尔滨工业大学数字逻辑大作业 四个附加功能可直接上板运行

1.设计一个开锁密码至少为4位数字的密码锁 2.当开锁按键开关(可设置为8位或更多,其中只有4位有效,其余为虚设)的输入代码等于所设密码时启动开锁控制电路,用F1灯亮,F2灯灭表示开锁状态,并用数码管显示英文大写...

部分参考代码 (末尾附文件) module MiMaSuo ( input clk, input rst_n, input ling, input yi, input er, input san, input si, input wu, input liu, input qi, input ba, input jiu, ... out

verilog FPGA Vivado 数字密码锁设计 包含报告

修改密码:解锁后,用户应该能够通过输入相同的两次按键序列来修改密码并锁定系统如果第二个按钮顺序与第一个按钮序列不匹配,则系统应保持解锁状态并显示错误消息 3.锁定后,用户应该能够通过输入锁定。2.修改密码:解锁...

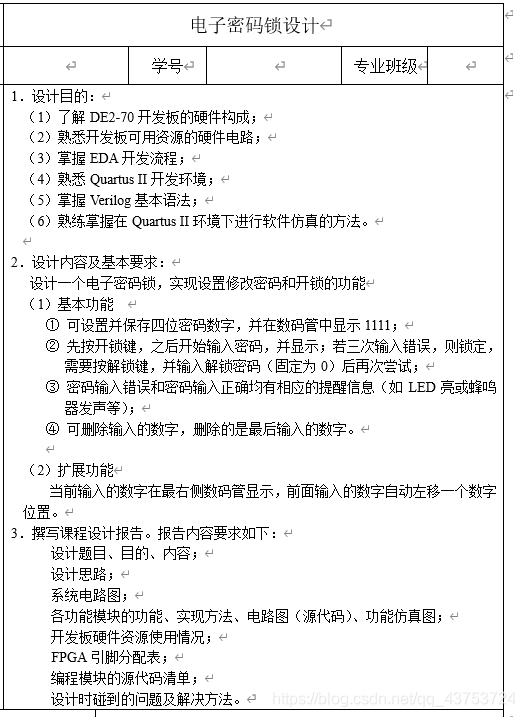

设计一个电子密码锁,实现设置修改密码和开锁的功能 ① 可设置并保存四位密码数字,并在数码管中显示1111; ② 先按开锁键,之后开始输入密码,并显示;若三次输入错误,则锁定,需要按解锁键,并输入解锁密码(固定...

本文详细介绍了数字密码锁的Verilog设计、仿真和上板验证流程。通过实现密码输入、检测和门锁控制的功能模块,并使用仿真和上板验证来验证设计的正确性,我们可以确保密码锁系统能够按预期工作。这个基于Verilog的...

开锁时,依次输入数字,当按下“确定”键时,如果在输入的一串数字中有连续 6位是正确密码,则给出开锁指示信息;当密码不符时,给出错误指示信息。 C. 用户需要修改密码时, 应先开锁,再按“设密码” 键,然后通过...

开锁时,依次输入数字,当按下“确定”键时,如果在输入的一串数字中有连续 6 位是正确密码,则给出开锁指示信息;当密码不符时,给出错误指示信息。 C. 用户需要修改密码时, 应先开锁,再按“设密码” 键,然后...

用verilog写的密码锁,在quartusII上仿真成功

基于硬件描述语言Verilog编写的可编程器件CPLD数字密码锁程序,用QuartusII软件打开工程文件,管脚的分配需根据自己具体的开发板去分配。

名称:数字密码锁Verilog代码Quartus远程云端平台(文末获取)软件:Quartus语言:Verilog代码功能:电子密码锁通过开关控制是否开始输入密码可以通过按键控制输入密码密码输入错误则报警输入密码10秒内没有开锁则...

基于FPGA的数字密码锁设计。内含设计报告、verilog源程序、EGO1电路图

四位密码,4x4矩阵键盘输入, ...按E显示密码,进入修改密码模式,按数字输入新密码,再次按E退出修改密码 RTL文件夹是程序文件,SIM文件夹是仿真文件,如果软件不对应可以使用这两个文件夹文件新建工程

FPGA数字密码锁.zip

标签: 硬件描述语言

基于FPGA的智能电子密码锁设计,电子密码锁设计也是现在研究比较广泛的一类设计,里面是完整的相关设计的代码,运用的是Verilog HDL语言。

设计一种数字密码锁,密码由3为十进制数字组成,初始设定为“000”。可由用户任意设置密码,密码输入正确时开锁,密码连续输入错误3次报警。

密码锁是一种常见的电子产品,采用Verilog状态机可以实现密码锁的设计。Verilog是一种硬件描述语言,它可以用于描述数字电路的结构和行为。 密码锁的Verilog状态机可以分为以下几个状态:初始状态、输入密码状态、...

wire clr,clkp,btnall; wire [3:0]bn; wire [31:0]sw; assign sw='h55556666; assign btnall=btn[0]|btn[1]|btn[2]|btn[3]|btn[4]|btn[5]|btn[6]|btn[7];...assign bn[3]=btn[7];...assign bn[2]=btn[3]|btn[4]|btn[5]|...

FPGA密码锁是一种利用FPGA芯片实现的数字密码锁系统。它通过Verilog HDL语言编写的主控部分,包括消除同步模块、计数器模块和控制器模块,取代了传统复杂的电路设计,简化了调试步骤。[1]该密码锁系统主要利用软件...

数电课程设计———虚位数字密码锁SWJTU verilog hdl语言 芯片CYCLONE IV E

绍了一种基于可编程逻辑器件FPGA的电子密码锁的设计方法,具有性能可靠、使用方便以及良好的...重点阐述了红外遥控解码、密码锁的解锁、密码修改等功能的实现,给出了数字密码锁的电路原理图及各模块的波形仿真结果。

推荐文章

- 机器学习之超参数优化 - 网格优化方法(随机网格搜索)_网格搜索参数优化-程序员宅基地

- Lumina网络进入SDN市场-程序员宅基地

- python引用传递的区别_php传值引用的区别-程序员宅基地

- 《TCP/IP详解 卷2》 笔记: 简介_tcpip详解卷二有必要看吗-程序员宅基地

- 饺子播放器Jzvd使用过程中遇到的问题汇总-程序员宅基地

- python- flask current_app详解,与 current_app._get_current_object()的区别以及异步发送邮件实例-程序员宅基地

- 堪比ps的mac修图软件 Pixelmator Pro 2.0.6中文版 支持Silicon M1_pixelmator堆栈-程序员宅基地

- 「USACO2015」 最大流 - 树上差分_usaco 差分-程序员宅基地

- Leetcode #315: 计算右侧小于当前元素的个数_找元素右边比他小的数字-程序员宅基地

- HTTP图解读书笔记(第六章 HTTP首部)响应首部字段_web响应的首部内容-程序员宅基地